ATSAMC21 Xplained Pro CAN bus example troubleshooting

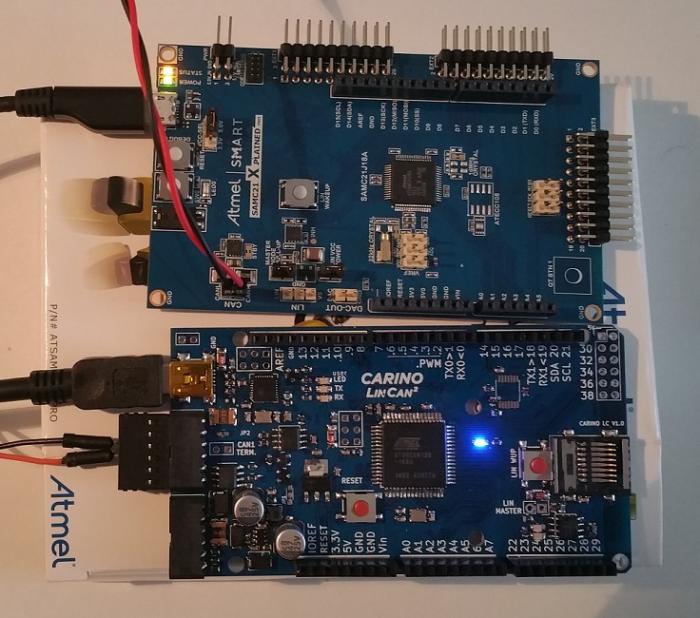

Second session with the SAMC21 Xplained Pro board showed another small trouble. CAN bus example does not work as intended. When trying "Quick Start for the SAM CAN Driver - SAM C21 Xplained Pro" hopes were that everything will work out of the box. SAMC21 Xplained Pro board was hooked up to CARINO LC. Trying to send data from SAMC21 resulted in a failure. SAMC21 was giving an error message (with some spelling mistakes of course:)) . The error message looked like this: "Protocal error, please double check the clock in two boards". After doing what is advised, baud rates on both devices (SAMC21 and CARINO LC) were set to 500kbps. This means one of the following: either CARINO LC or SAMC21 boards do not work as intended. Even though CARINO LC was tested in various environments, its functionality was rechecked with another development board (ATSAM4E Xplained Pro). Communication was working without problems, which lead to the second assumption. Something is wrong with the SAMC21 board or its firmware.

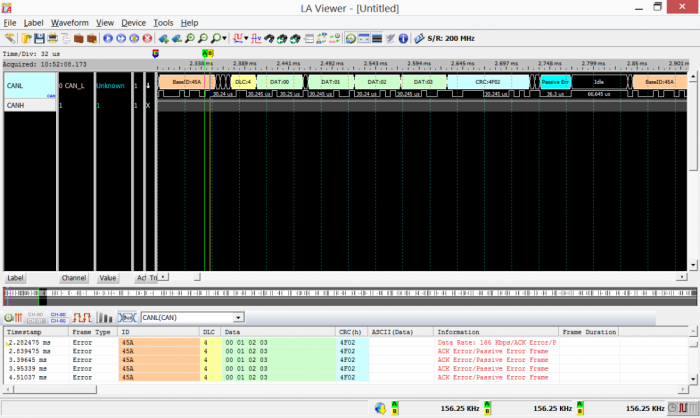

When troubleshooting these kind of problems some extra tools might come handy. It takes much more time to figure out what is wrong with the firmware or hardware when doing it only theoretically. Luckily, there was a logic analyzer nearby. It is possible to record various digital signals for further analysis. In this case we will look at the packet structure and timing.

Recording the CAN package coming out of SAMC21 board showed two things. The CAN packet structure was correct. However, the baud rate was 166kbps in stead of 500kbps. Which is approximately 3 times lower than it was supposed to be. No doubts - there is something wrong with clock settings on the SAMC21 board.

After few hours of digging in the source code and reading the datasheet, it is OK to state that there is an error in the initialization. First, looking at the CAN configuration header file (conf_can.h) you can see that CAN baud rate calculation was based on 48MHz CAN clock. There is some confusion in the source code and the way clocks are distributed. However, to tell what is going on in a few sentences:

CAN module needs to have two clocks - CAN bus clock (CLK_CANx_AHB) and generic clock GCLK_CANx. Generic clock frequency (GCLK_CANx) has to be equal or lower than the CAN bus clock (CLK_CANx_AHB). By default, the CAN bus clock frequency is set to the CPU clock domain frequency this is set to 48MHz by DPLL. This is OK. However, the GCLK_CANx clock is routed from generic clock 8 (GCLK_8). And clock for this one is coming from internal 48MHz generator, which has its output frequency divided by 3. This gives 16MHz clock for the GCLK_CANx clock. This messes up the CAN bus baud rate calculation and gives only 166kbps baud rate.

A quick fix for this problem is setting the internal 48MHz generator output frequency to 48MHz by changing the line 56 in conf_clocks.h file:

# define CONF_CLOCK_OSC48M_FREQ_DIV SYSTEM_OSC48M_DIV_3

to

# define CONF_CLOCK_OSC48M_FREQ_DIV SYSTEM_OSC48M_DIV_1

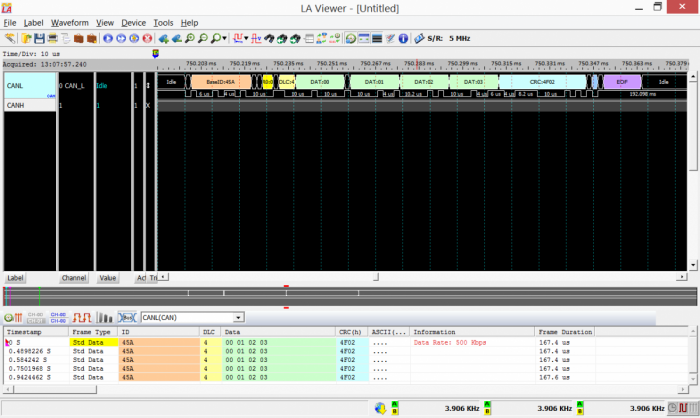

And here we have a success! Logic analyzer shows 500kbps baud rate and the SAMC21 Xplained Pro does not complain when sending the CAN messages.

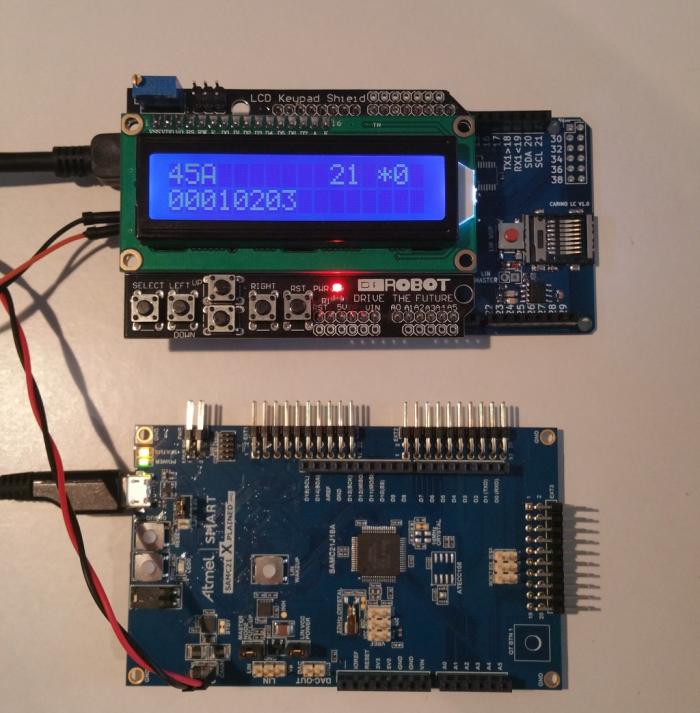

Even better - CARINO LC sees the messages sent from SAMC21 Xplained Pro board:

Comments

Add new comment